Разделы

Полезные сайты

Счетчики

ISSCC 2010: энергосберегающие технологии для электронных компонентов

Схема с сайта www.3dnews.ru

На очередной ежегодной международной конференции по твердотельной электронике International Solid State Circuits Conference (ISSCC) ряд компаний отрасли представили свои разработки, позволяющие сократить уровень энергопотребления компонентов. Среди них – Toshiba, ARM, Intel, NTT, Qualcomm и другие.

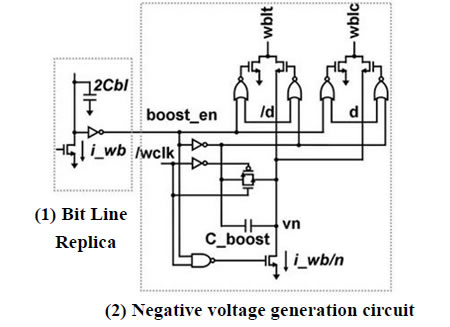

Решения Toshiba предназначены для создания усовершенствованных блоков статической памяти с произвольным доступом (static random access memories, SRAM), способных стабильно работать при пониженном напряжении питания. По данным Toshiba, предложенная ей усовершенствованная технология изготовления схем SRAM с пониженным напряжением питания позволяет решить наиболее актуальную для данного класса устройств проблему, снизив интенсивность ошибок при питающем напряжении 0,7 В на четыре порядка. Компания заявила, что разработанный ей дизайн SRAM готов для применения в системах автоматизированного проектирования компонентов, что позволит производителям микросхем сократить время на разработку и подготовку продукции к выпуску.

ARM сосредоточилась на технике, позволяющей оптимизировать работу построенных на базе ее архитектуры компонентов, и снизить потребляемую мощность вдвое, согласно заявлениям компании. Исследователи из ARM и Университета Мичигана представили гибридную технику динамического обнаружения и коррекции ошибок, получившую название Razor, благодаря которой, как заявлено, удалось добиться 52% снижения потребляемой мощности для 65-нм ARM-архитектуры, работающей на частоте более 1 ГГц. Описание характеризует Razor как сочетание схем обнаружения временных ошибок, механизмов коррекции ошибок и оптимизации напряжения и частот. Сообщается, что в отличие от других решений аналогичного назначения, системы с использованием Razor способны «выживать» при быстро изменяющихся параметрах окружения, адаптируясь к превалирующим условиям, что позволяет задействовать избыточные на текущий момент резервные ресурсы.

Документы, представленные на конференции компанией Intel, описывают решения, позволяющие на 12-23% снизить энергопотребление 45-нм 1,3 ГГц микропроцессорного ядра, используя схемы обнаружения ошибок, настраиваемые копии электрических цепей и схемы коррекции ошибок, предназначенные для смягчения динамически изменяемых защитных полос частот.

Исследователи из NTT представили 90-нм двухъядерный сетевой процессор, разработанный под техпроцесс CMOS и способный работать в качестве шлюза с полосой пропускания 2 Гбит/с, с поддержкой функций безопасности и фильтрации пакетов. Заявлено, что благодаря переносу значительной части операций по обработке пакетов на специализированную подсистему, уровень энергопотребления компонентf не будет превышать 24 мВт.

Информация с сайта www.3dnews.ru со ссылкой на eetimes.com.

Автор оригинального текста: Александр Харьковский.