Разделы

Полезные сайты

Счетчики

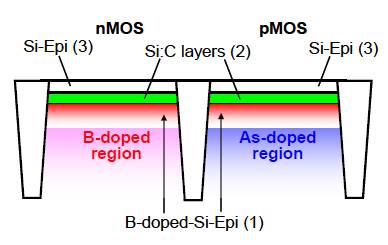

Toshiba предложила технологию для 20-нм КМОП полупроводников

Изображение с сайта www.3dnews.ru

Компания Toshiba заявила о разработке новой технологии создания слоев кремния с включениями примесей, которая, по ее словам, позволит решить ключевые проблемы, связанные с использованием недорогой комплементарной логики на КМОП-транзисторах для производства чипов по 20-нм нормам. Технология была представлена в ходе Международной встрече по электронным устройствам в Балтиморе – одной из крупнейших мировых конференций, посвященных полупроводникам.

Новая технология предполагает формирование трех слоев в канале: эпитаксиального кремния, кремния, легированного углеродом (Si:C), и слоя Si:C, легированного бором. При этом верхний слой эпитаксиального кремния выполняет роль проводника с низким сопротивлением для электронов и дырок; средний слой Si:C препятствует диффузионному распространению примеси, а нижний слой Si:C, легированный бором, подавляет утечки, вызванные формированием слоя Si:C. По данным Toshiba, применение новой структуры позволяет получить выигрыш в производительности на 15-18% по сравнению с традиционными технологиями. Предложенная структура может быть использована для формирования как nMOS, так и pMOS транзисторов, причем переход на ее использование требует внесения всего лишь нескольких относительно простых этапов в обычный процесс изготовления CMOS-чипов.

Информация с сайта www.3dnews.ru со ссылкой на toshiba.co.jp.

Автор оригинального текста: Александр Харьковский.