Разделы

Полезные сайты

Счетчики

Создан чип многослойной флэш-памяти емкостью 32 Гбит

Фото с сайта www.3dnews.ru

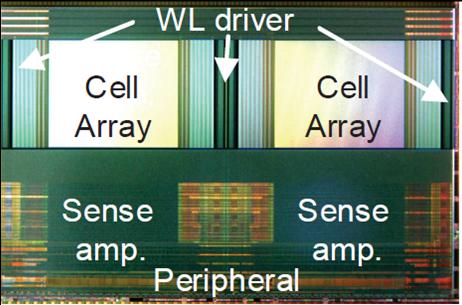

Toshiba Corp. представила многослойную флэш-память с двумя битами на ячейку типа P-BiCS (Pipe-shaped Bit Cost Scalable). Компанией был создан прототип 32-Гбит чипа, состоящий из 16 слоев ячеек памяти, изготовленных по 60-нм техпроцессу, который соответствует их матричной технологии производства. Он имеет размеры 10,11 х 15,52 мм с эффективной площадью ячейки на каждый бит 0,00082 мкм2, что меньше, чем у 32-нм флэш-памяти, запускаемой в производство в 2009 году.

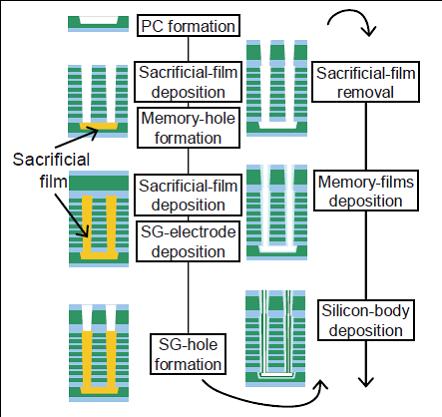

P-BiCS является улучшенной версией BiCS, трехмерная многослойная структура модуля флэш-памяти разрабатывалась Toshiba с 2007 года. BiCS использует технологию стеков ячеек памяти в многоуровневой структуре, чередующей укладку управляющего электрода в виде пленки и промежуточного диэлектрика, а в отверстие, проходящее через все эти слои, помещается поликристаллический кремниевый канал. При этом компания изменила форму NAND-цепочек для обеспечения многоуровневого процесса и его контроля на уровне массива. В BiCS ячейки соединены в прямолинейную NAND-цепочку, а для P-BiCS была выбрана U-образная форма. Кроме того, существуют два наиболее значимых достижения в их структуре.

Первое, поскольку качество туннельно-изолирующей пленки повышено, была улучшена способность к хранению данных, реализуя многоуровневый процесс. Качество туннельно-изолирующей пленки улучшилось за счет того, что отпала необходимость ее удаления с нижней стороны сквозного отверстия. В BiCS туннельно-изолирующая пленка, формируемая на стороне сквозного отверстия, повреждается во время этого процесса, часто ухудшая запоминающие свойства. Toshiba представила метод снижения вероятности повреждения путем смены материала туннельно-изолирующей пленки с оксида кремния на нитрид кремния. Однако пока компания не может гарантировать достаточных запоминающих свойств при использовании нитрида кремния, заявляют ее представители.

Второе, поскольку свойства селекторного транзистора и линейного источника, используемых для чтения и записи данных, улучшены, рабочая характеристика на уровне массива стала более жесткой. В BiCS, которая имеет прямолинейную форму цепочки, селекторный транзистор и линейный источник расположены на нижней части цепочки. С другой стороны, в P-BiCS, чьи цепочки имеют U-образную форму, они могут быть сосредоточены в конце цепочки. Поэтому, когда цепочка формируется, температура порядка 1 тыс. °С не прикладывается к селекторному транзистору или линейному источнику. В результате запирающие свойства селекторного транзистора улучшаются, уменьшая число ошибок чтения.

В виду того, что металлические материалы могут применяться для линейного источника, скорость записи может быть выше, чем у BiCS. BiCS использует диффузионный слой, который стремится к высокому сопротивлению, как линейный источник. Когда сопротивление линейного источника высоко, колебание порогового напряжения становится значительным в этом массиве, что понижает скорость записи. Группа разработчиков P-BiCS намеревается организовать технологию серийного производства для многослойного модуля флэш-памяти в течение двух-трех лет в качестве меры по высокой интеграции флэш-модуля без использования микрообработки. И P-BiCS выглядит одним из главных кандидатов для осуществления этой цели.

Для дальнейшего снижения издержек требуется еще один прорыв, а именно, в методе укладки слоев", — говорит Хидеаки Аочи (Hideaki Aochi), ведущий специалист Отделения технологий передовых запоминающих устройств (Advanced Memory Device Technology Dept) и Центра исследований и разработки полупроводников (Center for Semiconductor Research & Development) Toshiba Corp. Например, сейчас отверстие может проходить одновременно через 8 уровней. А 16 уровней реализуются совмещением двух восьмислойных модулей. В будущем Toshiba планирует создать методику получения сразу 16 уровней и более.

Информация с сайта www.3dnews.ru со ссылкой на techon.nikkeibp.co.jp.

Автор оригинального текста: Андрей Горьев.