Разделы

Полезные сайты

Счетчики

1.3.3. Регистры

Регистры можно разделить на два класса - сдвигающие и хранения информации. В свою очередь, регистры хранения бывают «прозрачные», тактируемые импульсом, и синхронные, тактируемые фронтом импульса.

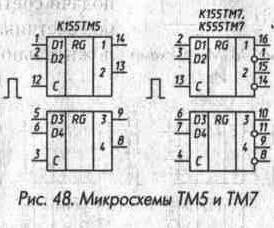

Микросхемы К155ТМ5 и ТМ7 (рис. 48) содержат по четыре триггера, образующих два двухразрядных регистра хранения информации. Каждый триггер имеет информационный вход D, тактовый вход С и прямой выход (а в микросхеме ТМ7 еще и инверсный выход). Триггер работает следующим образом. При лог. 0 на входе С изменение сигнала на входе D не влияет на состояние триггера и он хранит записанную в нем ранее информацию. При подаче на вход С лог. 1 триггер превращается в повторитель - сигнал на выходе соответствует сигналу на входе, за это свойство подобные триггеры называют «прозрачными». При подаче на вход С лог. 0 триггер переходит вновь в режим хранения, а его состояние определяется сигналом на входе D перед спа-

дом импульса на входе С. Таким образом, основные свойства триггеров микросхем К155ТМ5 и ТМ7 следующие:

1) при подаче на вход С лог. 0 - хранение информации;

2) при подаче на вход С лог. 1 - повторение входного сигнала;

3) запоминается информация, имеющаяся на входе D перед спадом на входе С;

4) изменение информации на выходе может происходить в течение всего положительного импульса на входе С, если при этом меняется информация на входе D.

Эту разновидность D-триггера называют «D-триггером, тактируемым импульсом», «триггером-защелкой», «прозрачным» триггером, чтобы отличать ее от описанных выше D-триггеров ТМ2, которые можно назвать «D-триггерами, тактируемыми фронтом» или «синхронными D-триггерами».

Для того чтобы подчеркнуть различие между ними, приведем логику работы D-триггера, тактируемого фронтом импульса:

1) хранение информации осуществляется при подаче на вход С как лог. 0, так и лог. 1;

2) прямое прохождение сигнала на выход со входа D нет;

3) запоминается информация, имеющаяся на входе D перед фронтом импульса положительной полярности на входе С;

4) изменение информации на выходе может происходить только во

время фронта на входе С.

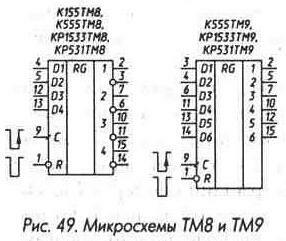

Микросхема ТМ8 (рис. 49) - регистр хранения информации, содержащий четыре синхронных D-триггера, по функционированию анало

гичных триггерам микросхем ТМ2. Сброс триггеров происходит при подаче лог. 0 на вход R, запись - по спаду импульса отрицательной полярности на входе С. Информация на входах D1 - D4 может меняться как при лог. 0, так и при лог. 1 на входе С, она важна лишь непосредственно перед изменением сигнала на входе С с лог. 0 на лог. 1. Микросхема ТМ9 - регистр хране

ния информации, содержащий шесть D-триггеров, по функционированию аналогичных триггерам микросхем ТМ2 и ТМ8.

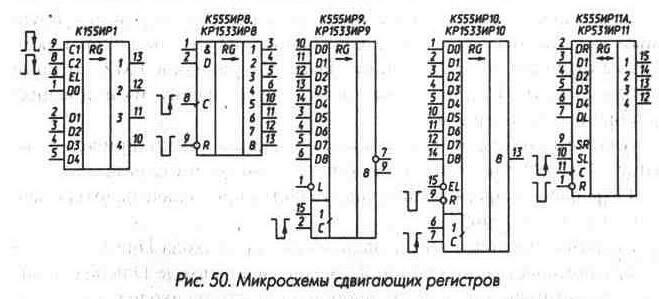

Микросхема К155ИР1 (рис. 50) - четырехразрядный сдвигающий регистр, позволяет производить последовательную и параллельную запись информации в триггеры регистра, последовательное и параллельное считывание информации, сдвиг информации. Вход С1 микросхемы служит для подачи положительных тактовых импульсов, сдвигающих информацию, причем сдвиг происходит по спадам импульсов. При подаче положительного импульса на вход С2 по его спаду происходит запись в триггеры регистра информации, имеющейся на входах D1 - D4. Кроме того, есть управляющий вход EL. Запись со входов D1 - D4 может происходить лишь при наличии лог. 1 на входе EL, сдвиг - при наличии лог. 0. Для последовательной записи информации используется вход D0, запись происходит в режиме сдвига.

Наличие управляющего входа EL расширяет возможности использования микросхемы. Если соединить между собой входы С1 и С2, можно управлять сдвигом и записью, лишь изменяя логический уровень на входе EL. Можно соединить между собой входы С2 и EL, специального управляющего сигнала в этом случае не потребуется -сдвиг будет происходить при подаче импульсов на вход С1, запись -при подаче импульсов на С2.

Если вход D1 подключить к выходу 2, D2 - к выходу 3, D3 - к выходу 4, а D4 использовать в качестве входа последовательной записи, то получится реверсивный сдвигающий регистр. При подаче импульсов на вход С1 будет происходить последовательная запись информации со входа D0 и сдвиг в сторону возрастания номеров выходов (сдвиг вправо). При подаче импульсов на вход С2 запись будет происходить со входа D4, сдвиг - в сторону уменьшения номеров выходов (сдвиг влево). В полученный таким образом реверсивный сдвигающий регистр параллельная запись информации невозможна.

Микросхема К555ИР8 (рис. 50) - восьмиразрядный сдвигающий регистр. Она имеет вход С для подачи импульсов сдвига, вход сброса R, два равноправных входа D для подачи сдвигаемой информации, собранных по И, и восемь выходов. Обнуление триггеров регистра производится подачей лог. 0 на вход R. Прием информации со входов D и ее сдвиг в сторону выходов с большими номерами происходят по спадам импульсов отрицательной полярности на входе С.

Микросхему К555ИР8 удобно использовать для преобразования информации, поступающей в последовательном коде, в параллельный.

Микросхема К555ИР9 (рис. 50) - восьмиразрядный сдвигающий регистр с возможностью асинхронной параллельной записи и последовательным считыванием. Микросхема имеет вход D0 для подачи

информации при последовательной записи, восемь входов D1 - D8 для подачи информации при параллельной записи, два равноправных входа для подачи тактовых импульсов (выводы 2 и 15), вход параллельной записи L и прямой и инверсный выходы последнего разряда сдвигающего регистра. Переключение триггеров регистра происходит по спаду импульсов отрицательной полярности на любом из входов С при лог. 0 на другом. Подача лог. 1 на любой из входов запрещает переключение триггеров при подаче импульсов на второй вход. Режим работы регистра определяется сигналом, поданным на вход L - при лог. 1 на нем по спадам импульсов на входе С происходит сдвиг информации, поступающей на вход D0, выходам 8, при лог. 0 на входе L происходит параллельная запись информации со входов D1 - D8 в триггеры регистра.

Микросхема К555ИР10 (рис. 50) по своей структуре аналогична микросхеме К555ИР9 и отличается от нее синхронной параллельной записью, отсутствием инверсного выхода последнего разряда сдвигающего регистра и наличием входа R для сброса всех триггеров регистра в нулевое состояние. Сброс производится при подаче лог. 0 на вход R, запись - спадом импульса отрицательной полярности на входе С при лог. 0 на входе EL.

Микросхемы К555ИР9 и К555ИР10 удобно применять для преобразования параллельного кода в последовательный. Наличие двух входов для подачи тактовых импульсов позволяет использовать один из них как вход разрешения работы регистра, другой - для выполнения сдвига или записи.

Микросхема ИР11 (рис. 50) - универсальный четырехразрядный сдвигающий регистр, позволяет производить как параллельную запись информации, так и ее сдвиг вправо и влево. Имеет входы: D1 -D4 - для подачи информации при параллельной записи; DR - при последовательной записи и сдвиге вправо (в сторону возрастания номеров выходов); DL - то же и сдвиге влево; SR и SL - управляющие, С - для подачи тактовых импульсов и R - сброса.

При подаче лог. 0 на вход R происходит установка триггеров регистра в 0. При лог. 1 на входе R режим работы определяется управляющими сигналами на входах SR и SL При лог. 1 на входе SR и лог. 0 на входе SL по спадам импульсов отрицательной полярности на входе С происходит последовательный прием информации с входа DR и сдвиг вправо. При лог. 1 на входе SL и лог. 0 на входе SR происходит прием информации с входа DL и сдвиг влево. При лог. 1 на обоих входа SR и SL по спаду импульса отрицательной полярности на входе С произойдет параллельная

запись информации со входов D1 - D4. Если на входах SR и SL лог. 0, переключение триггеров регистра при изменении информации на входе С не происходит.

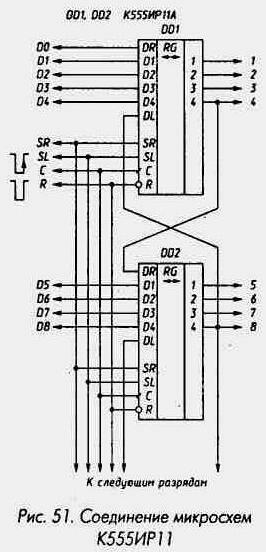

Соединение микросхем ИР11 в многоразрядный реверсивный сдвигающий регистр проиллюстрировано на рис. 51.

Микросхема КР531ИР12 (рис. 52) -четырехразрядный сдвигающий регистр. Имеет четыре прямых выхода 1-4, инверсный выход разряда 4 и следующие входы: R - сброса, С - для подачи тактовых импульсов, EL - установки режима параллельной записи, J и К - для подачи информации при последовательной записи и D1, D2, D3, D4 - для подачи информации при параллельной записи.

Вход сброса R - преобладающий - при подаче на него лог. 0 независимо от состояния других входов все триггеры микросхемы устанавливаются в 0. Если на входе R лог. 1, возможна запись информации

в триггеры микросхемы. При лог. 0 на входе EL по спаду импульса отрицательной полярности на входе С произойдет запись информации с входов J и К в триггер с выходом 1 и сдвиг информации в остальных триггерах в сторону возрастания номеров выходов. Информация, которая будет записана в первый триггер, определяется состоянием входов J и К перед спадом импульса отрицательной полярности на входе С. Если объединить между собой входы J и К, будет записываться информация, имеющаяся на

этих объединенных входах. Если на вход J подать лог. 0, на вход К -лог. 1, изменения информации в первом триггере по спаду импульса отрицательной полярности на входе С не произойдет. При лог. 1 на входе J и лог. 0 на входе К первый триггер микросхемы переходит в счетный режим и меняет свое состояние на противоположное на каждый спад импульса отрицательной полярности на входе С.

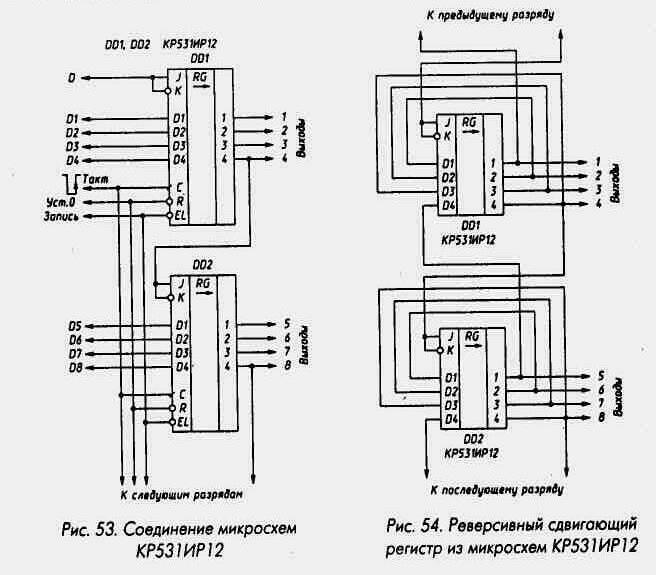

Для построения сдвигающего регистра с числом разрядов более четырех достаточно соединить выходы четырех микросхем младших

разрядов с объединенными входами J и К микросхем следующих разрядов (рис. 53). Входы С, R, EL различных микросхем следует соединить между сбой.

Для построения реверсивного сдвигающего регистра выходы и информационные входы микросхем следует соединить между собой в соответствии с рис. 54, параллельная запись информации в такой регистр невозможна, а сигнал на входах EL микросхем будет определять направление сдвига.

Микросхема К155ИР13 (рис. 55) - восьмиразрядный реверсивный сдвигающий регистр, имеет 8 выходов параллельного кода и следующие входы: D1 - D8 - для подачи информации при параллельной записи, DR и DL - для подачи информации при последовательной записи и сдвиге вправо и влево соответственно, С - для подачи тактовых импульсов, SR и SL - для управления режимом и R - для сброса триггеров регистра.

При подаче на вход R лог. 0 происходит сброс всех триггеров счетчика независимо от состояния других входов. Любые другие изменения состояния регистра происходят лишь по спаду импульса отрицательной

полярности на входе С. При лог. 1 на входе SR и лог. 0 на входе SL по спаду импульса на входе С происходит сдвиг информации вправо (в сторону возрастания номеров выходов). В первый разряд сдвигающего регистра последовательный прием информации осуществляется со входа DR. При лог. 1 на входе SL и лог. 0 на входе SR сдвиг осуществляется влево, прием информации в восьмой разряд регистра - со входа DL. Если лог. 1 подать сразу на оба входа SR и SL, по спаду импульса отрицательной полярности на входе С произойдет параллельная запись в регистр информации со входов D1 - D8.

Подача лог. 0 на оба входа SR и SL блокирует тактовые импульсы, подаваемые на вход С, и по ним информация в регистре уже не будет меняться. Однако, если при лог. 0 на входе С вначале хотя бы на одном из входов SR или SL имелась лог. 1, затем на обоих входах - лог. 0, это изменение будет воспринято микросхемой как спад тактового импульса, по которому произойдет сдвиг или параллельная запись, в зависимости от состояния входов SR и SL перед появлением лог. 0 на обоих входах. Указанное свойство микросхемы позволяет, подав постоянно лог. 0 на вход С, использовать вход SR для подачи импульсов сдвига вправо, вход SL - для подачи импульсов сдвига влево. Сдвиг будет происходить по спадам импульсов положительной полярности. Если изменение сигнала с лог. 1 на лог. 0 произойдет одновременно на обоих входах SR и SL, осуществится параллельная запись информации со входов D1 - D8.

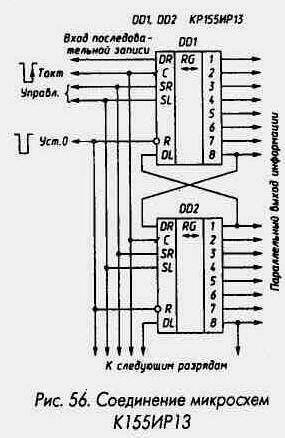

Соединение микросхем К155ИР13 для увеличения разрядности проиллюстрировано на рис. 56.

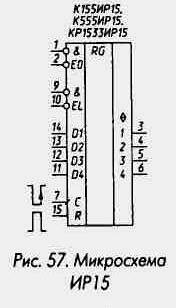

Микросхема ИР15 (рис. 57) - четырехразрядный регистр хранения информации с возможностью перевода выходов в высокоимпедансное состояние. Запись информации со входов D1 - D4 в триггеры микросхемы происходит по спаду импульса отрицательной полярности на входе С, обнуление триггеров - по импульсу положительной полярности на входе R. Особенность регистра - два равноправных инверсных входа разрешения записи EL, собранных по И. Наличие лог. 1 на любом из этих входов запрещает запись в триггеры, причем изменение сигналов на входах D1 - D4 может происходить как при лог. 0, так и при лог. 1 на входе С, важно лишь состояние этих входов непосредственно перед переходом сигнала на входе С из лог. 0 в лог. 1.

Микросхема имеет два равноправных инверсных входа ЕО, собранных по И. Наличие лог. 1 на любом из этих входов переводит

выходы в высокоимпедансное состояние. Состояние входов ЕО никак не влияет на работу микросхемы по другим входам - запись, обнуление могут происходить при любых сочетаниях сигналов на входах ЕО.

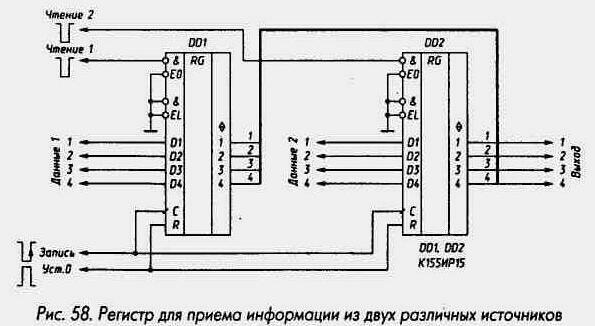

Основное назначение микросхемы -прием, хранение и мультиплексирование информации, поступающей от различных источников. В качестве простейшего примера на рис. 58 приведена схема для обеспечения одновременного приема четырехразрядной информации от двух различных источников Данные 1 и Данные 2 по фронту импульса на входе Запись и поочередной передачи принятой информации на выход по сигналам Чтение 1 и Чтение 2.

Наличие двух входов разрешения записи и двух входов перевода в высокоимпедансное состояние позволяет легко организовать матричное управление большим числом микросхем. Например, два описываемых далее дешифратора ИД4 могут управлять по входам ЕО матрицей из 64 микросхем ИР15, в результате можно получить одновременный прием и запоминание 256 бит информации и последовательную передачу информации по 4 бита в необходимом порядке.

Управляя матрицей по входам EL, можно организовать последовательный прием информации

от различных источников и параллельную выдачу, если выходы микросхем не объединять.

Микросхема К555ИР16 (рис. 59) - четырехразрядный сдвигающий регистр с возможностью перевода выходов в высокоимпедансное состояние, имеет входы: D0 - для подачи последовательной информации при сдвиге; D1 - D4 - для подачи информации при параллельной записи;

С - для тактовых импульсов; EL - для выбора режима параллельной записи и ЕО - для перевода выходов в высокоимпедансное состояние.

При лог. 1 на входе EL спад импульса положительной полярности на входе С приводит к параллельной записи информации со входов

D1 - D4 в триггеры регистра. Если на входе EL лог. 0, по спадам на входе С происходит прием информации со входа D0 и сдвиг ее в сторону возрастания номеров выходов.

Подача лог. 0 на вход ЕО приводит к переводу выходов регистра в высокоимпедансное состояние, при котором сдвиг информации невозможен. Параллельная запись возможна как при лог. 0, так и при лог. 1 на входе ЕО.

Микросхема К555ИР16 по логике своей работы близка к микросхеме К155ИР1 и в ряде случаев может заменить ее без существенной переработки печатных плат, так как назначение выводов микросхем К555ИР16 и К155ИР1 совпадает, за исключением вывода 8.

Микросхема К155ИР17 (рис. 60) - специальный регистр, предназначенный для построения аналого-цифровых преобразователей, работающих по принципу последовательного приближения с числом разрядов до 12. Имеет четыре входа:

С - для подачи тактовых импульсов (срабатывание триггеров регистра происходит по спаду тактовых импульсов отрицательной полярности), D - для подачи запоминаемой регистром информации, Е - разрешения преобразования и ER - сброса.

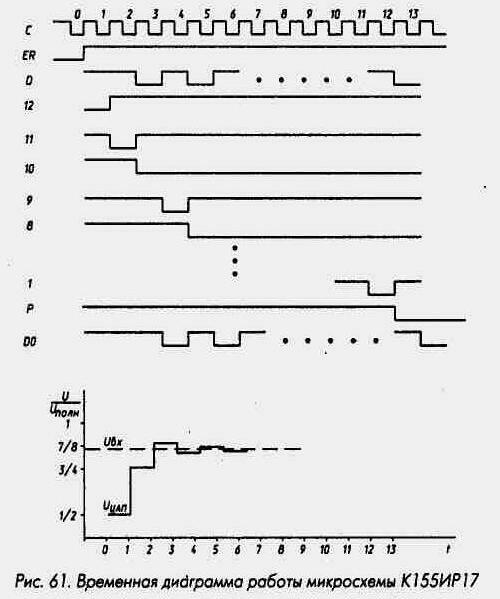

Работа микросхемы проиллюстрирована на диаграммах C-DO рис. 61. При подаче на вход ER лог. 0 по спаду очередного импульса отрицательной полярности (импульс 0) происходит начальная установка

триггеров регистра - на выходе 12 устанавливается лог. 0, на выходах 1-11 и 12 - лог. 1. На выходе окончания преобразования Р появляется лог. 1. Такое состояние регистра будет сохраняться до тех пор, пока на входе ER будет лог. 0.

После установления на входе ER лог. 1 первый спад импульса отрицательной полярности произведет запись в триггер регистра с выходами 12 и 12 информации со входа D и установит выход 11 в состояние 0, на выходах 10-1 и Р будет лог. 1. Спад очередного импульса отрицательной полярности произведет запись информации со входа D в очередной триггер регистра и установит следующий за ним выход в состояние 0. Таким образом, на выходах регистра поочередно появляется лог. 0, вслед за ним - информация со входа D.

После записи информации со входа D в последний триггер регистра (с выходом 1) на выходе Р появляется лог. 0 и это состояние регистра фиксируется до появления лог. 0 на входе ER. Если вход ER соединить с выходом Р, появление лог. 0 на выходе Р по спаду очередного

тактового импульса (импульс 13 на рис. 61) приведет к установлению исходного состояния регистра аналогично импульсу 0. В результате микросхема будет повторять описанный выше цикл работы с периодом 13 тактов.

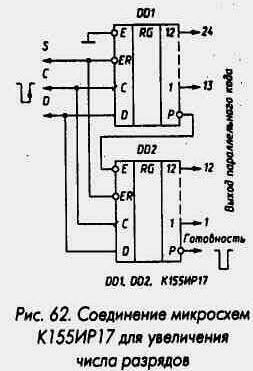

Так микросхема работает при лог. 0 на входе Е. Если на вход Е подать лог. 1, выходы 12-1 и Р переходят в состояние 1 и на сигналы на других входах не реагируют. Наличие входа Е позволяет соединять между собой микросхемы для получения регистров последовательного приближения на 24,36 и т. д. разрядов (рис. 62). Работа таких регистров аналогична работе одной микросхемы, а период при соединении выхода Р последней микросхемы с объединенными входами ER всех

микросхем составит 25,37 и т. д. тактов.

Микросхема позволяет использовать ее в качестве регистра последовательного приближения и с меньшим, чем на 12, числом разрядов, для чего для подачи сигнала на вход ER можно использовать его соединение с любым из выходов 1-11.

Если вход D подключить постоянно к источнику лог. 1, микросхему можно использовать как счетчик с дешифратором, на выходах которого поочередно на период тактовых импульсов появляется лог. 0. Коэффициент пересчета счетчика составит 13, он может быть и меньше при соединении входа ER с любым из выходов 11-1.

Если на вход D постоянно подавать лог. 0, микросхема будет работать так, что по каждому тактовому импульсу на очередном из выходов 11-1 регистра лог. 1 будет изменяться на лог. 0, который будет держаться на выходе до конца цикла. На выходе 12 при этом будет постоянно лог. 0. Длительность цикла также может быть переменной - от 2 до 13 периодов тактовых импульсов.

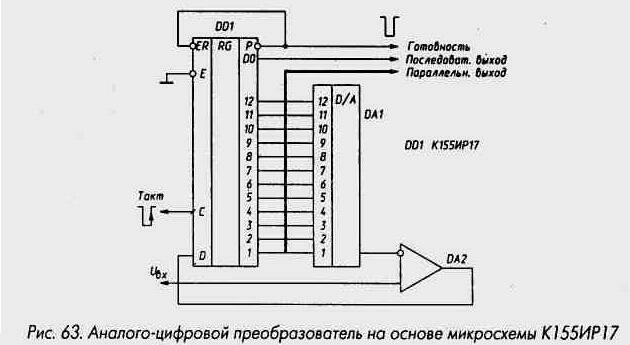

Основное же назначение микросхемы К155ИР17 - построение аналого-цифровых преобразователей (АЦП). Одна из возможных схем АЦП приведена на рис. 63. К выходам 12-1 микросхемы подключен цифро-аналоговый преобразователь (ЦАП) DA1, старший разряд - 12, младший - 1. Компаратор DA2 сравнивает выходное напряжение ЦАП и преобразуемое в код входное напряжение.

Работает АЦП следующим образом. Тактовый импульс 0 устанавливает, как уже указывалось, выход 12 микросхемы DD1 в 0, остальные

выходы - в 1. В результате на вход ЦАП подается код 0111...1, на его выходе формируется напряжение, равное половине преобразуемого диапазона входных напряжений. Компаратор DA2 сравнивает его с входным, и если входное напряжение превышает напряжение с выхода ЦАП, как это показано на нижней диаграмме рис. 61, на его выходе появляется лог. 1. Тактовым импульсом 1 лог. 1 записывается в триггер микросхемы с выходом 12, это состояние триггера сохраняется до конца преобразования (диаграмма 12 рис. 61). Если входное напряжение меньше половины диапазона преобразователя, в триггер с выходом 12 запишется лог. 0.

По окончании тактового импульса 1 на выходе 11 микросхемы DD1 появится лог. 0 и на ЦАП будет подан код 10111...1 (для примера, показанного на рис. 61). В результате входное напряжение будет сравниваться с 3/4 преобразуемого диапазона входных напряжений. Если, как показано на рис. 61, входное напряжение больше, чем 3/4 диапазона, в триггер с выходом 11 будет записана 1, в противном случае - 0. Для описываемого примера в триггер регистра с выходом 11 импульс 2 запишет 1, и на ЦАП будет подан код 11011...1. В результате входное напряжение будет сравниваться с 1/2 + 1/4 + 1/8 =7/8 полного диапазона, если оно меньше, в триггер с выходом 10 запишется 0. По окончании такта 12 на выходах 12-1 микросхемы образуется двоичный двенадцатиразрядный код преобразованного напряжения, для данного случая 110101...1. Лог. 0 на выходе Р сигнализирует об окончании преобразования и может быть использован для переписи сформированного кода в регистр хранения. Если, как указывалось выше, выход Р

соединить с выходом ER, преобразование будет производиться циклически с периодом 13 тактов входных импульсов.

В процессе преобразования на выход D0 микросхемы выдается сдвинутая на один период входных импульсов информация со входа D, являющаяся последовательным кодом преобразованного входного напряжения.

Разрядность АЦП может быть уменьшена, если использовать вместо выхода Р любой из выходов 11-1, и увеличена, если микросхемы К155ИР17 соединить в соответствии с рис. 62 и использовать ПАП соответствующей разрядности.

Микросхему К155ИР17 можно использовать также и для других операций, производимых методом последовательных приближений. Например, при наличии цифрового умножителя кодов можно построить устройство, извлекающее квадратные корни или производящее деление одного цифрового кода на другой. Для извлечения квадратного корня микросхема выдает «пробное» значение корня 011...1, которое с помощью цифрового умножителя кодов возводится в квадрат и цифровым компаратором сравнивается с кодом числа, из которого надо извлечь корень. Далее работа происходит аналогично работе АЦП, в результате чего на выходе можно получить код квадратного корня. Аналогично можно производить деление или определение кода обратного числа.

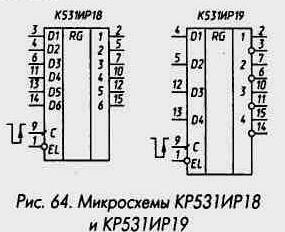

Микросхема КР531ИР18 - шестиразрядный регистр хранения информации (рис. 64). Запись информации в регистр производится по спаду импульса отрицательной полярности на входе С, при этом на входе разрешения записи EL должен быть лог. 0. Если на входе EL лог. 1, запись в регистр запрещена.

Микросхема КР531ИР19 (рис. 64) - четырехразрядный регистр хранения информации с прямыми и инверсными выходами, функционирует аналогично микросхеме КР531ИР18.

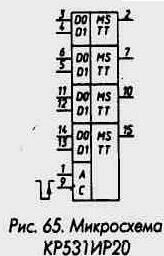

Микросхема КР531ИР20 (рис. 65) -четыре двухвходовых мультиплексора с регистром хранения на выходе. На входы регистра поступают сигналы со входов D0 микросхемы, если на адресном входе А лог. 0, и со входов D1, если на входе А лог. 1. Запись в регистр производится по спаду импульса отрицательной полярности на входе С. По функционированию эта микросхема близка

описываемой далее микросхеме КП13 (для КП13 запись происходит по спаду импульса положительной полярности), разводка выводов у них разная.

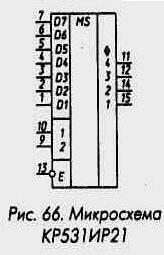

Микросхема КР531ИР21 (рис. 66) не является регистром. Это комбинационная микросхема статического сдвигателя четырехразрядного кода, по логике функционирования она ближе всего к мультиплексорам. Микросхема имеет семь информационных входов D1-D7, два адресных 1 и 2 и вход разрешения Е. Выходы 1-4 выполнены с возможностью их перевода в высокоимпедансное состояние при подаче на вход Е лог. 1, выходы активны при лог. 0 на входе Е.

На выходы 1-4 проходят сигналы с соответствующего входа, номер которого увеличен на десятичный эквивалент двоичного кода, поданного на входы 1 и 2. Если, например, на входах 1 и 2 лог. 0, на выходы проходят сигналы со входов D1 - D4, если на входе 1 - лог. 1, на входе 2 - лог. 0 - со входов D2 - D5, если и на входе 1, и на входе 2 -лог. 1 - со входов D4 - D7.

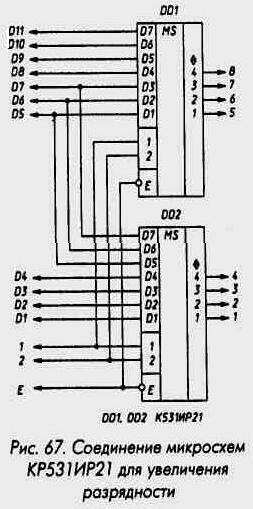

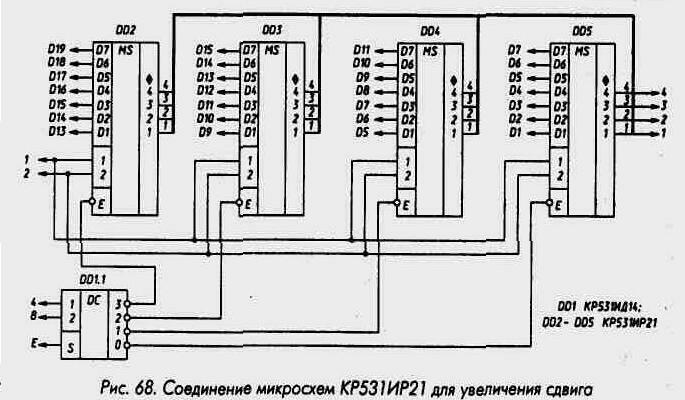

Если необходимо сдвигать восьмиразрядный код, микросхемы КР531ИР21 следует соединять в соответствии с рис. 67. Если же необходим сдвиг более чем на три разряда, микросхемы можно объединить согласно рис. 68. Дешифратор DD1 в зависимости от старших разрядов сдвига 4 и 8 выбирает одну из микросхем DD2 -DD5, выбор входных сигналов внутри микросхемы осуществляют младшие разряды сдвига 1 и 2.

Микросхемы КР531ИР21 находят применение в комбинационных умножителях и других случаях. Допустимое значение выходного тока микросхем в состоянии лог. 0 стандартное - 20 мА, в состоянии лог. 1 -6,5 мА при выходном напряжении 2,4 В. Входные токи в состоянии лог. 0 по входам D2 и D6 - 4 мА, D3 и D5 - 6 мА, D4 - 8 мА.

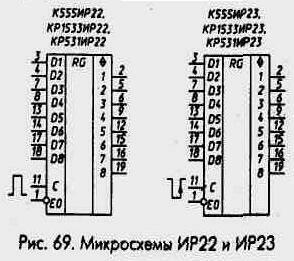

Микросхема ИР22 (рис. 69) - восьмиразрядный регистр хранения информации, тактируемый импульсом, с возможностью перевода выходов в высокоимпедансное состояние. Запись информации в триггеры регистра происходит при подаче лог. 1 на вход С, в этом случае сигналы на выходах регистра повторяют входные, регистр <<прозрачен» для сигналов на входах D1 - D8. При подаче лог. 0 на вход С регистр переходит в режим хранения информации.

Выходы микросхемы находятся в активном состоянии, если на вход ЕО подан лог. 0. Если же на вход ЕО подать лог. 1,выходы регистра переходят в высокоимпедансное состояние. Сигнал на входе ЕО не влияет на запись в триггеры, запись может производиться как при лог. 0, так и при лог. 1 на этом входе.

Микросхема ИР23 (рис. 69) - синхронный регистр хранения информации - отличается от ИР22 тем, что

запись информации производится по спаду импульса отрицательной полярности на входе С. Информация на входах D1-D8 может меняться как при лог. 0, так и при лог. 1 на входе С, важна она лишь непосредственно перед переходом сигнала на входе С с лог. 0 в лог. 1.

Нагрузочная способность микросхем К555ИР22 и К555ИР23 в три раза превышает стандартную для микросхем серии К555, для микросхем

КР1533ИР22 и КР1533ИР23 максимальный уровень лог. 0 0,4 В при втекающем токе 12 мА и 0,5 В при 24 мА, уровень лог. 1 2,4 В - при вытекающем токе 2,6 мА и 2,5 В при 0,4 мА. Для микросхем КР531ИР22 и КР1531ИР23 значение выходного тока в состоянии лог. 0 стандартное - 20 мА, в состоянии лог. 1 - 6,5 мА при выходном напряжении 2,4 В. Входные токи в состоянии лог. 0 составляют 0,25 мА.

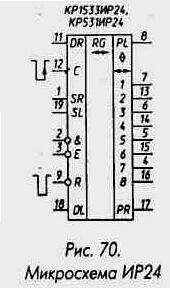

Микросхема ИР24 - восьмиразрядный реверсивный сдвигающий регистр со входами параллельной записи, совмещенными с выходами (рис. 70). Микросхема имеет восемь триггеров с выходными ключами, которые могут переводиться в высокоимпедансное состояние (выходы ключей на рис.70 обозначены 1-8), от первого и последнего триггеров сделаны также выходы переноса PL и PR. Управляются выходные ключи по двум равноправным входам Е, сбрасываются триггеры по асинхронному входу сброса R. Все другие изменения состояния триггеров производятся по спадам им-

пульсов отрицательной полярности, подаваемых на вход С.

Преобладающие над другими - входы R, Е. Подача лог. 0 на вход R устанавливает все триггеры регистра в 0 независимо от состояния других входов. Подача хотя бы одной лог. 1 на входы Е переводит основные выходы 1-8 в высокоимпедансное состояние независимо от сигналов на других входах. Выходы PL и PR - стандартные, они всегда находятся в активном состоянии.

Режим работы регистра при лог. 1 на входе R и подаче импульсов на вход С выбирают по входам SR и SL. При подаче лог. 1 на вход SR и лог. 0 на вход SL по спадам импульсов отрицательной полярности происходит сдвиг информации вправо (вниз по рис. 70), запись в разряд 1 происходит со входа DR, при лог. 0 на входе SR и лог. 1 на входе SL - влево, запись в разряд 8 - со входа DL. При подаче лог. 0 на оба входа SR и SL по импульсам на входе С изменение состояния триггеров не происходит. Во всех этих случаях состояние (активное или высокоимпедансное) выходов 1-8 определяется сигналами на входах Е. Если же на входы SR и SL подана лог. 1, выходы 1-8 переходят в высокоимпедансное состояние независимо от сигналов на входах Е и по спадам импульсов отрицательной полярности на входе С происходит параллельная запись в регистр информации, поступающей на его выходы 1-8 (теперь они стали входами).

Микросхему ИР24 удобно использовать для преобразования последовательного кода в параллельный и наоборот, для параллельного

приема многоразрядного двоичного числа, его сдвига в любую сторону на необходимое число разрядов и выдачи на ту же шину и во многих других случаях.

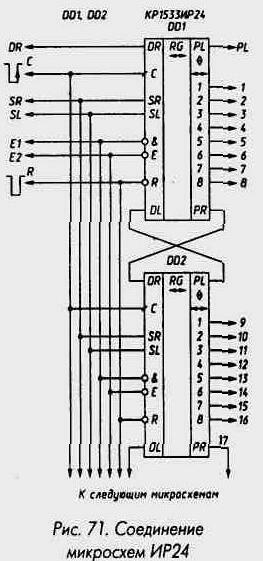

На рис. 71 приведена схема соединения микросхем между собой для увеличения числа разрядов.

Нагрузочная способность микросхем КР1533ИР24 по выходам 1-8 такая же, как и у КР1533ИР22, по выходам PR и PL - стандартная. Для микросхемы КР531ИР24 максимально допустимый выходной ток по выходам 1-8 в состоянии лог. 0-20 мА, в состоянии лог. 1 -6,5 мА при 2,4 В и 0,5 мА - при 2,7 В. По выходам PL и PR максимальный ток в состоянии лог. 0 составляет 6 мА. Входные токи в состоянии лог. 0 по выводам 1-7,11-16, 18, 19 составляют 0,25 мА.

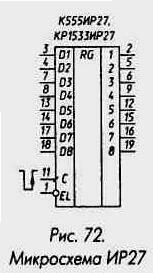

Микросхема К555ИР27 (рис. 72)-восьмиразрядный регистр хранения информации. Запись информации в регистр производится, как и для микросхемы

ИР23, по спаду импульса отрицательной полярности на входе С. Регистр имеет инверсный вход разрешения записи EL, при лог. 1 на этом входе запись в регистр запрещена. Информация на входах D1 - D8 может меняться как при лог. 0, так и при лог. 1 на входе С.

Регистры ТМ8, ТМ9, ИР15, ИР22, ИР23, К555ИР27 могут использоваться для кратковременного запоминания небольшого объема информации, поступающей в параллельном коде.

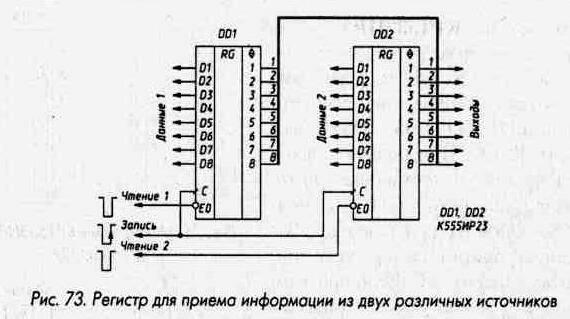

Выходы микросхем ИР22 и ИР23 можно объединять, что позволяет организовать не только запоми

нание информации, но и ее мультиплексирование. Для примера на рис. 73 приведена схема приема восьмибитовой информации одновременно от двух различных источников Данные 1 и Данные 2, подобная рис. 58. Поочередная выдача информации на выходы может осуществляться при подаче на входы Чтение 1 и Чтение 2 лог. 0.

При необходимости из микросхем ТМ8, ТМ9, ИР23, К555ИР27 можно построить сдвигающий регистр, соединив входы D2 - D8

соответственно с выходами 1-7, в такой сдвигающий регистр параллельная запись информации невозможна.

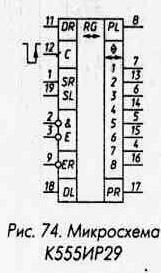

Микросхема КР1533ИР29 - восьмиразрядный реверсивный сдвигающий регистр (рис. 74), работает аналогично микросхеме КР1533ИР24. Однако в нем обеспечивается еще и синхронный сброс. Для установки триггера регистра в нулевое состояние на вход разрешения установки ER нужно подать лог. 0, а на вход С - импульс отрицательной полярности. Сброс триггеров произойдет по спаду импульса.

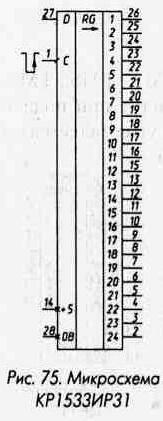

Микросхема КР1533ИР31 - 24-разрядный сдвигающий регистр (рис. 75) Она имеет два входа (D - информационный и С - тактовый) и 24 выхода. Последовательная запись информации со входа и ее сдвиг происходят по спадам импульсов отрицательной полярности, поступающих на вход С Отличие подачи питания от стандартного варианта специально отмечено на графическом обозначении микросхемы Микросхема удобна для преобразования длинного последовательного кода в параллельный.

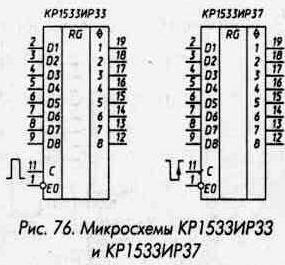

Микросхема КР1533ИРЗЗ (рис 76) по функционированию и нагрузочной способности соответствует КР1533ИР22, отличается от нее разводкой выводов, мощностью и быстродействием

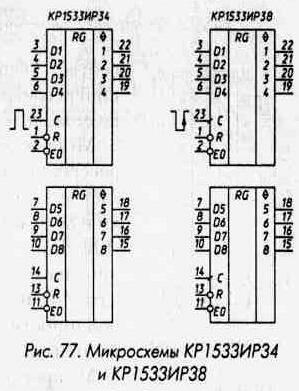

Микросхема КР1533ИР34 - два

четырехразрядных регистра хранения (рис. 77). Каждый из регистров, кроме четырех входов для подачи информации D1 - D4 (D5 - D8), имеет входы С, R, ЕО. При подаче на вход R лог. 0 происходит установка триггеров регистра в состояние 0 независимо от сигналов на других входах Запись информации происходит при подаче лог. 1 на вход С. Если при этом на вход ЕО подан лог. 0, триггеры регистра «прозрачны» и выходные сигналы повторяют входной сигнал, запоминание сигналов происходит в момент подачи лог. 0 на вход С. Подача лог. 1 на вход ЕО приводит к переводу выходов в высокоимпедансное состояние, но не мешает записи информации в триггеры регистра. Нагрузочная способность микросхемы КР1533ИР34 такая же, как у КР1533ИР22.

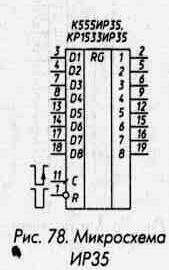

Микросхема К555ИР35 - восьмиразрядный регистр хранения информации (рис. 78) Логика работы триг-

геров регистра такая же, как и у микросхем ТМ2, ТМ8, ТМ9. Установка триггеров в нулевое состояние происходит при подаче лог 0 на вход R, параллельная запись информации осуществляется по

спаду импульсов отрицательной полярности, подаваемых на вход С Нагрузочная способность микросхемы стандартная.

Микросхема КР1533ИР37 (рис. 76) аналогична по функционированию и нагрузочной способности КР1533ИР22, отличается разводкой выводов, мощностью и быстродействием

Микросхема КР1533ИР38 (рис 77) отличается от КР1533ИР34 тем, что триггеры ее регистров синхронны - запись в них происходит по спаду импульсов отрицательной полярности на входе С.